Difference between revisions of "Beta Debug Shield"

m (update links) |

|||

| (11 intermediate revisions by 2 users not shown) | |||

| Line 1: | Line 1: | ||

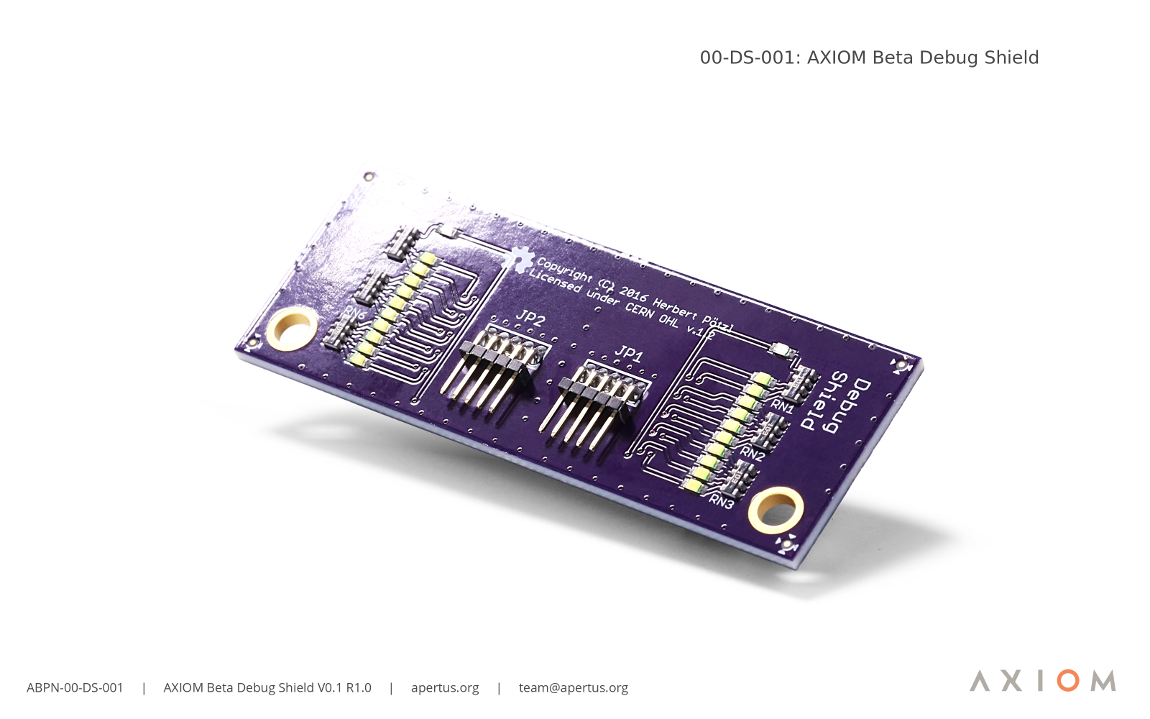

[[File: | [[File:00-DS-001- AXIOM Beta Debug Shield V0.1R1.0 Show sm.jpg | 1150px |]] | ||

[https://wiki.apertus.org/images/a/aa/00-DS-001-_AXIOM_Beta_Debug_Shield_V0.1R1.0_Show.jpg Full size image] | |||

[[AXIOM Beta]] features two shield-slots with space for additional connectors going to both east and west sides of the camera. One shield has a slow-speed (200Mb/s) interface and one medium-speed (1Gbit/s) interface connecting to the main processing FPGA. Therefore these shields are perfect for additional future interfaces like: Trigger in/out, Genlock in/out, Timecode in/out, Sync in/out or connecting external sensors or buttons, small LCDs, etc. The name "shields" was inspired by the Arduino plugin boards - also called "shields". | |||

* Compatible with both East and West shield headers. | |||

* Via East shield header has four high-speed LVDS pairs (1Gbit/s). | |||

* Via West shield header has four medium-speed LVDS pairs (200Mb/s+). | |||

* 20x GPIO bank LED indicators. | |||

* 2x Power LEDS. | |||

* AC coupling and biasing via pull-ups and pull-downs. | |||

* Shields are not hot pluggable. | |||

See [[Beta Main Board]] for specifics on how shields are utilised and [[AXIOM_Beta/Camera_Structure | Camera Structure]] for an overview on how PCBs are stacked. | |||

[[File:ABCS-DS-02a- AXIOM Beta Debug Shield V0.1R1.0 Top Populated sm.jpg | 1150px |]] | |||

[https://wiki.apertus.org/images/6/6b/ABCS-DS-02a-_AXIOM_Beta_Debug_Shield_V0.1R1.0_Top_Populated.jpg Full size image] | |||

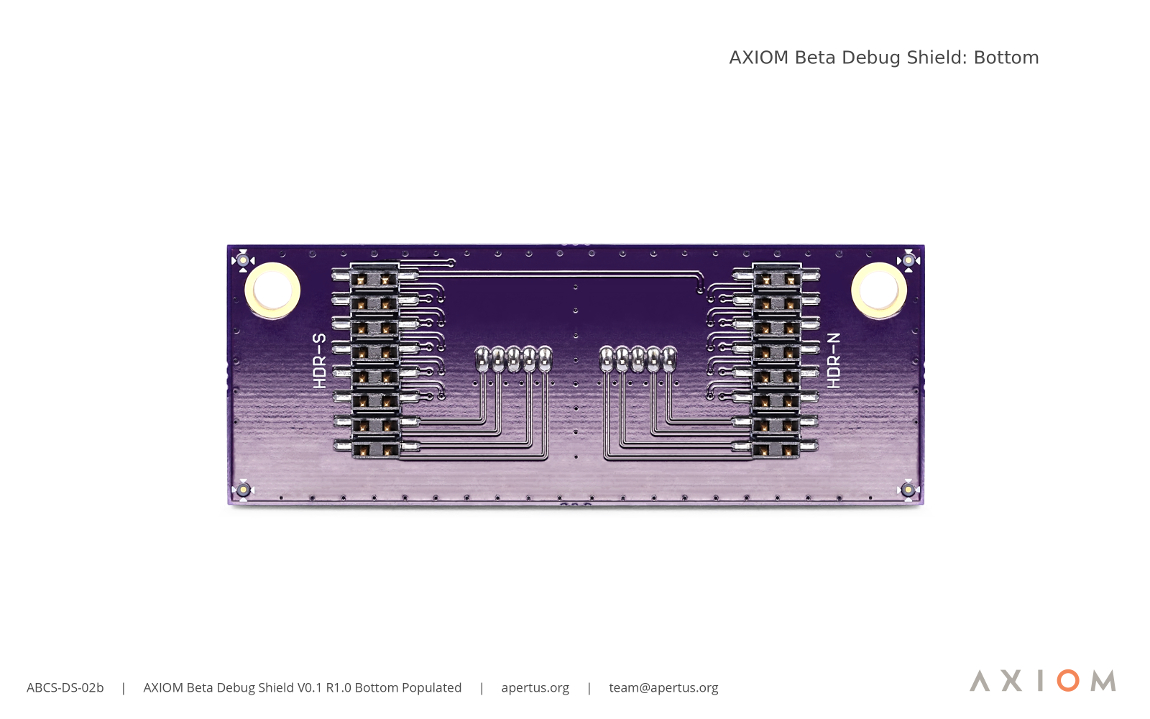

[[File:ABCS-DS-02b- AXIOM Beta Debug Shield V0.1R1.0 Bottom Populated sm.jpg | 1150px |]] | |||

[https://wiki.apertus.org/images/1/1c/ABCS-DS-02b-_AXIOM_Beta_Debug_Shield_V0.1R1.0_Bottom_Populated.jpg Full size image] | |||

===Current Revision=== | |||

Sources: https://apertus-open-source-cinema.github.io/pcbs/index.html#/boards/AXIOM%20Beta%20Shield%20Debug/ | |||

https://wiki.apertus.org/index.php/AXIOM_Beta_Debug_Shield_V0.1_R1.0 | |||

Latest revision as of 17:04, 18 December 2021

AXIOM Beta features two shield-slots with space for additional connectors going to both east and west sides of the camera. One shield has a slow-speed (200Mb/s) interface and one medium-speed (1Gbit/s) interface connecting to the main processing FPGA. Therefore these shields are perfect for additional future interfaces like: Trigger in/out, Genlock in/out, Timecode in/out, Sync in/out or connecting external sensors or buttons, small LCDs, etc. The name "shields" was inspired by the Arduino plugin boards - also called "shields".

- Compatible with both East and West shield headers.

- Via East shield header has four high-speed LVDS pairs (1Gbit/s).

- Via West shield header has four medium-speed LVDS pairs (200Mb/s+).

- 20x GPIO bank LED indicators.

- 2x Power LEDS.

- AC coupling and biasing via pull-ups and pull-downs.

- Shields are not hot pluggable.

See Beta Main Board for specifics on how shields are utilised and Camera Structure for an overview on how PCBs are stacked.

Current Revision

Sources: https://apertus-open-source-cinema.github.io/pcbs/index.html#/boards/AXIOM%20Beta%20Shield%20Debug/

https://wiki.apertus.org/index.php/AXIOM_Beta_Debug_Shield_V0.1_R1.0