Difference between revisions of "SDI Plugin Module"

m |

|||

| (33 intermediate revisions by 2 users not shown) | |||

| Line 1: | Line 1: | ||

__NOTOC__ | __NOTOC__ | ||

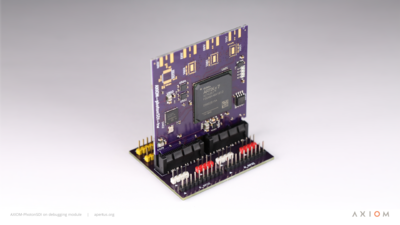

[[File:00-DSDI-001- AXIOM-Photon-SDI R1.0 Top Populated Show sm.jpg | 1150px |]] | |||

[https://wiki.apertus.org/images/b/bf/00-DSDI-001-_AXIOM-Photon-SDI_R1.0_Top_Populated_Show.jpg Full size image.] | |||

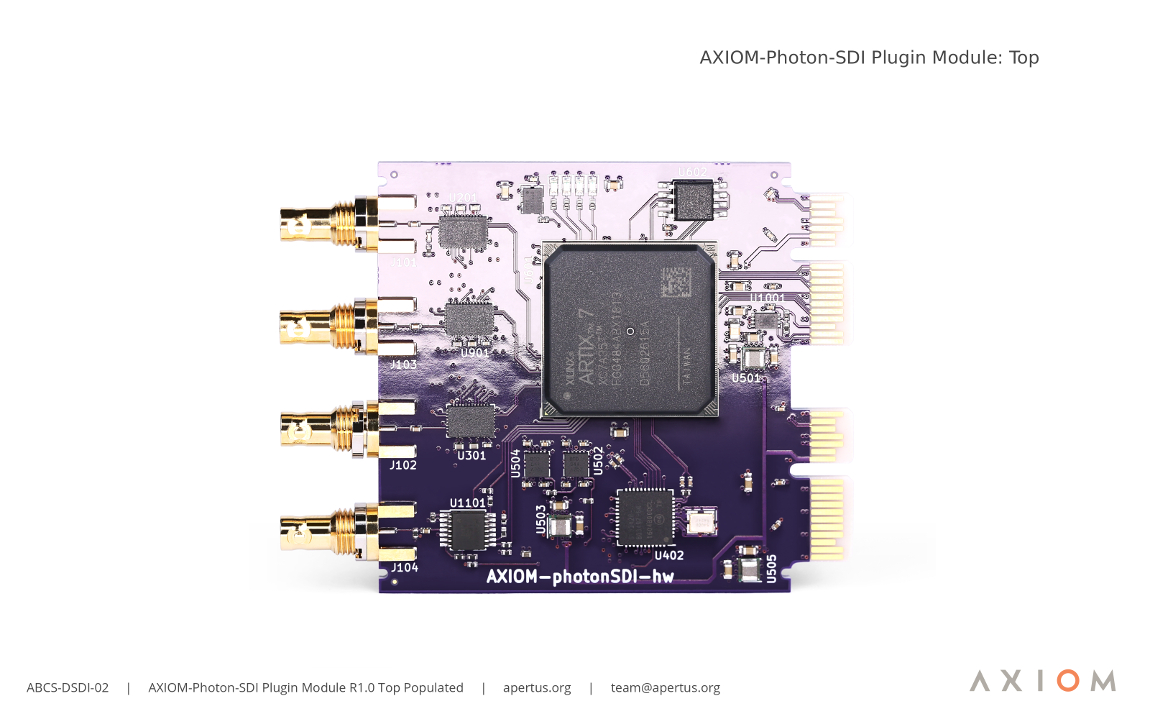

[[File: | AXIOM photonSDI is an extension board that's designed to utilise both available module slots on AXIOM Beta Main Board adding 6G SDI connectivity to the camera's features. | ||

The board has two independent 6G SDI outputs that can both output the same image, different images, or be used in a dual 6G configuration that allows the transmission of 4k video material at 60 frames per second. Additionally the board contains a 6G SDI input for synchronisation and blending and a legacy synchronisation input. | |||

* [https://www.xilinx.com/products/silicon-devices/fpga/artix-7.html XC7A35T] FPGA. | |||

** Gigabit Transceivers with up to 6 GBit/s -> HD/3G/6G SDI support. | |||

* 2x [https://www.semtech.com/products/broadcast-video/cable-drivers/GS12281 GS12281] SDI line driver and 1x GS12241 SDI equalizer. | |||

** Full data sheet publicly available. | |||

** Supports retiming of up to 12G SDI signals. | |||

* [https://www.silabs.com/timing/jitter-attenuators/high-performance/device.si5342b Si5342B] clock generator. | |||

** Very low jitter (90 fs rms). | |||

** Can be locked to reference signal. | |||

* [https://www.ti.com/product/LMH1981 LMH1981] sync separator. | |||

[[File:ABCS-DSDI-02 AXIOM-Photon-SDI R1.0 Top Populated sm.jpg | 1150px |]] | |||

[https://wiki.apertus.org/images/e/e4/ABCS-DSDI-02_AXIOM-Photon-SDI_R1.0_Top_Populated.jpg Full size image.] | |||

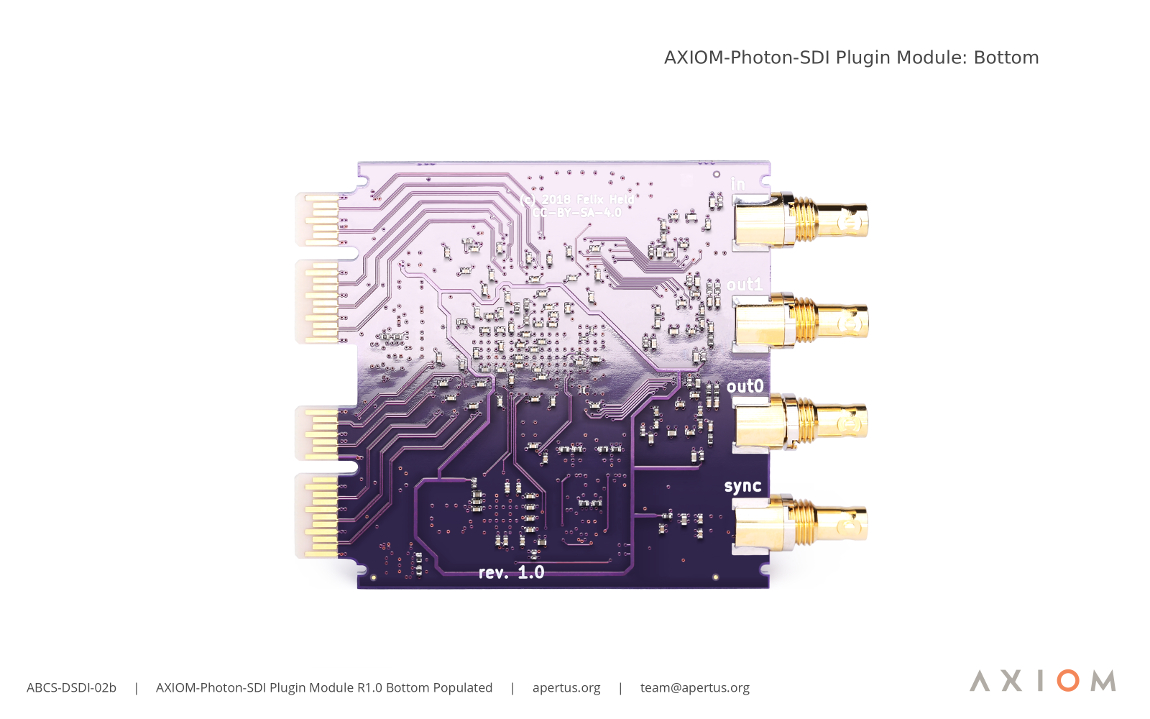

[[File:ABCS-DSDI-02b AXIOM-Photon-SDI R1.0 Bottom Populated sm.jpg | 1150px |]] | |||

[https://wiki.apertus.org/images/1/11/ABCS-DSDI-02b_AXIOM-Photon-SDI_R1.0_Bottom_Populated.jpg Full size image.] | |||

===How it works=== | ===How it works=== | ||

* A description of a desired SDI connectivity is created using the LiteX framework (a fork of Migen). | |||

* The framework generates a Hardare Description Language (HDL) reprensentation in Verilog. | |||

* The HDL is passed to the tool chain which generates a configuration for the chip on the evaluation SDI Extension Board. | |||

* The configuration is loaded onto the chip on a base board that is plugged into the camera. | |||

* Camera with chip has new functionality for connecting to professional SDI video equipment. | |||

<gallery mode="packed" heights="150"> | |||

Image:AXIOM Photon-SDI Top 16x9.png| AXIOM PhotonSDI PCB Top unpopulated. | |||

Image:AXIOM Photon-SDI Bot 16x9.png| AXIOM PhotonSDI PCB Bottom unpopulated. | |||

Image:AXIOM PhotonSDI Part Populated Top Debugging.png | AXIOM PhotonSDI PCB on custom debugging module. | |||

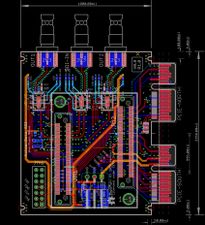

Image:11.2017. Duel 6G SDI Plugin Module.jpeg| Board file. | |||

</gallery> | |||

===Technical Details=== | |||

Implemented in: | |||

* Hardware description language loaded into chips | |||

* Litex, a Python framework for building custom hardware | |||

Supported hardware platforms: | |||

* Field programmable gate array (FPGA) evaluation board AC701 + SDI interface evaluation board TB-FMCH-12GSDI | |||

* apertus AXIOM Beta + SDI plugin module | |||

===License=== | |||

Source code is available on [https://github.com/felixheld/photonSDI GitHub]. | |||

PhotonSDI is released under the very permissive two-clause BSD license. Under the terms of this license you are authorized to use PhotonSDI for closed-source proprietary designs. Even though we do not require you to do these things, we'd be grateful if you did: | |||

* Tell us that you are using photonSDI. | |||

* Cite photonSDI in publications related to research it has helped. | |||

* Send us feedback and suggestions for improvements. | |||

* Send us bug reports when something goes wrong. | |||

* Send us the modifications and improvements you have done to photonSDI. | |||

[https://www.apertus.org/contact Contact form]. | |||

===Notes=== | ===Notes=== | ||

The initial development | The initial development was sponsored by the German Federal Ministry of Education and Research ([https://www.bmbf.de/en/index.html BMBF]) via their [https://prototypefund.de/en/ Prototype Fund]. | ||

An industry standard serial digital interface (SDI) connection plugin module will provide a nominal data transfer rate of 3G/6G. | An industry standard serial digital interface (SDI) connection plugin module will provide a nominal data transfer rate of 3G/6G. | ||

Projects using PhotonSDI: | Projects using PhotonSDI: AXIOM Beta, HDMI2USB, Numato Opsis. | ||

== Revisions== | |||

'''Current:''' | |||

https://wiki.apertus.org/index.php/AXIOM_PhotonSDI_Plugin_Module_v0.9 | |||

| Line 62: | Line 114: | ||

[[category: plugins]] | [[category: plugins]] | ||

[[category: Shields]] | [[category: Shields]] | ||

[[category: PhotonSDI]] | |||

[[category: SDI]] | |||

Latest revision as of 04:18, 15 January 2020

AXIOM photonSDI is an extension board that's designed to utilise both available module slots on AXIOM Beta Main Board adding 6G SDI connectivity to the camera's features.

The board has two independent 6G SDI outputs that can both output the same image, different images, or be used in a dual 6G configuration that allows the transmission of 4k video material at 60 frames per second. Additionally the board contains a 6G SDI input for synchronisation and blending and a legacy synchronisation input.

- XC7A35T FPGA.

- Gigabit Transceivers with up to 6 GBit/s -> HD/3G/6G SDI support.

- 2x GS12281 SDI line driver and 1x GS12241 SDI equalizer.

- Full data sheet publicly available.

- Supports retiming of up to 12G SDI signals.

- Si5342B clock generator.

- Very low jitter (90 fs rms).

- Can be locked to reference signal.

- LMH1981 sync separator.

1 How it works

- A description of a desired SDI connectivity is created using the LiteX framework (a fork of Migen).

- The framework generates a Hardare Description Language (HDL) reprensentation in Verilog.

- The HDL is passed to the tool chain which generates a configuration for the chip on the evaluation SDI Extension Board.

- The configuration is loaded onto the chip on a base board that is plugged into the camera.

- Camera with chip has new functionality for connecting to professional SDI video equipment.

2 Technical Details

Implemented in:

- Hardware description language loaded into chips

- Litex, a Python framework for building custom hardware

Supported hardware platforms:

- Field programmable gate array (FPGA) evaluation board AC701 + SDI interface evaluation board TB-FMCH-12GSDI

- apertus AXIOM Beta + SDI plugin module

3 License

Source code is available on GitHub.

PhotonSDI is released under the very permissive two-clause BSD license. Under the terms of this license you are authorized to use PhotonSDI for closed-source proprietary designs. Even though we do not require you to do these things, we'd be grateful if you did:

- Tell us that you are using photonSDI.

- Cite photonSDI in publications related to research it has helped.

- Send us feedback and suggestions for improvements.

- Send us bug reports when something goes wrong.

- Send us the modifications and improvements you have done to photonSDI.

4 Notes

The initial development was sponsored by the German Federal Ministry of Education and Research (BMBF) via their Prototype Fund.

An industry standard serial digital interface (SDI) connection plugin module will provide a nominal data transfer rate of 3G/6G.

Projects using PhotonSDI: AXIOM Beta, HDMI2USB, Numato Opsis.

5 Revisions

Current:

https://wiki.apertus.org/index.php/AXIOM_PhotonSDI_Plugin_Module_v0.9