Difference between revisions of "CMV12000"

| Line 40: | Line 40: | ||

Interestingly the signal values are not completely the same when using unity gain vs x3 combined with division by 3. The second option results in slightly higher levels. | Interestingly the signal values are not completely the same when using unity gain vs x3 combined with division by 3. The second option results in slightly higher levels. | ||

Values between the ones listed (2,4,5,6,10,12,13,14,16,17,..) | Values between the ones listed (2,4,5,6,10,12,13,14,16,17,..) result in undocumented float factors: | ||

2 -> ~1.2 | |||

4 -> ~1.1 | |||

5 -> ~2.1 | |||

6 -> ~1.2 | |||

10 -> ~0.4 | |||

11 -> ~1.1 | |||

==Register 116== | ==Register 116== | ||

Revision as of 13:38, 7 January 2014

1 Register 87 & 88

Signed 12 bit value (0..4095) for even/odd rows:

max offset: 2047 min offset: 2048

Default value:780

From the datasheet:

The value in this register defines the dark level offset applied to the bottom/top output signal (min = 0, max = 4095)

1824: 12 bits per pixel 533: 10 bits per pixel 600: 8 bits per pixel

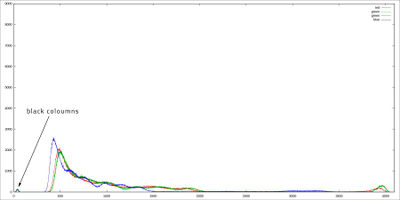

Using a higher offset shifts the black columns into the useable area (in this example 1980 was used as offset value for both top/bottom rows):

2 Register 102

from Application Note:

Lowering reg 102 [6:0] will reduce the spatial row noise, but will also decrease the black sun protection. When the protection is set to the default value of 120, it can influence the CDS working, causing increased FPN in the image. You should find a trade-off between the protection and the FPN. We see that a value of 100 should be OK for most applications.

Datasheet lists this register as "DO NOT CHANGE" with default value of "8312"

3 Register 115

Analog gain PGA_gain 115[2:0]

0: unity gain 1: x2 gain 3: x3 gain 7: x4 gain

PGA_div 115[3]

1: divide signal by 3

Gain and division can be combined to generate factors like x0.33, x0.66, slightly above 1 (see below), 1.33

Interestingly the signal values are not completely the same when using unity gain vs x3 combined with division by 3. The second option results in slightly higher levels.

Values between the ones listed (2,4,5,6,10,12,13,14,16,17,..) result in undocumented float factors:

2 -> ~1.2 4 -> ~1.1 5 -> ~2.1 6 -> ~1.2 10 -> ~0.4 11 -> ~1.1

4 Register 116

ADC_range 116[7:0] and ADC_range_mult 116[9:8]

Higher value creates flatter ADC slope. Lower values "compress" values together in the histogram.

Default value [9:0 - combined] (12bit): 1023

Values higher than 1023 (bin: 11 1111 1111) don't seem to have any effect on making the slope even flatter.

5 Register 117

DIG_gain 117[4:0]

Apply digital gain to signal 1: 12 bit 4: 10 bit 6: 8 bit

A digital factor to amplify the signal digitally.

value 0 has no effect.

values 1, 2, 3, 4, 6, 8, 10 have an effect and simply multiply the signal with the gives value.

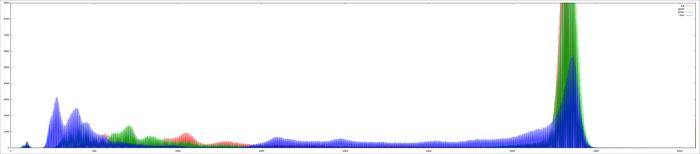

Note: A factor above 1 creates gaps between samples in the histogram: