Difference between revisions of "Beta Main Board"

(→About) |

|||

| (39 intermediate revisions by 3 users not shown) | |||

| Line 1: | Line 1: | ||

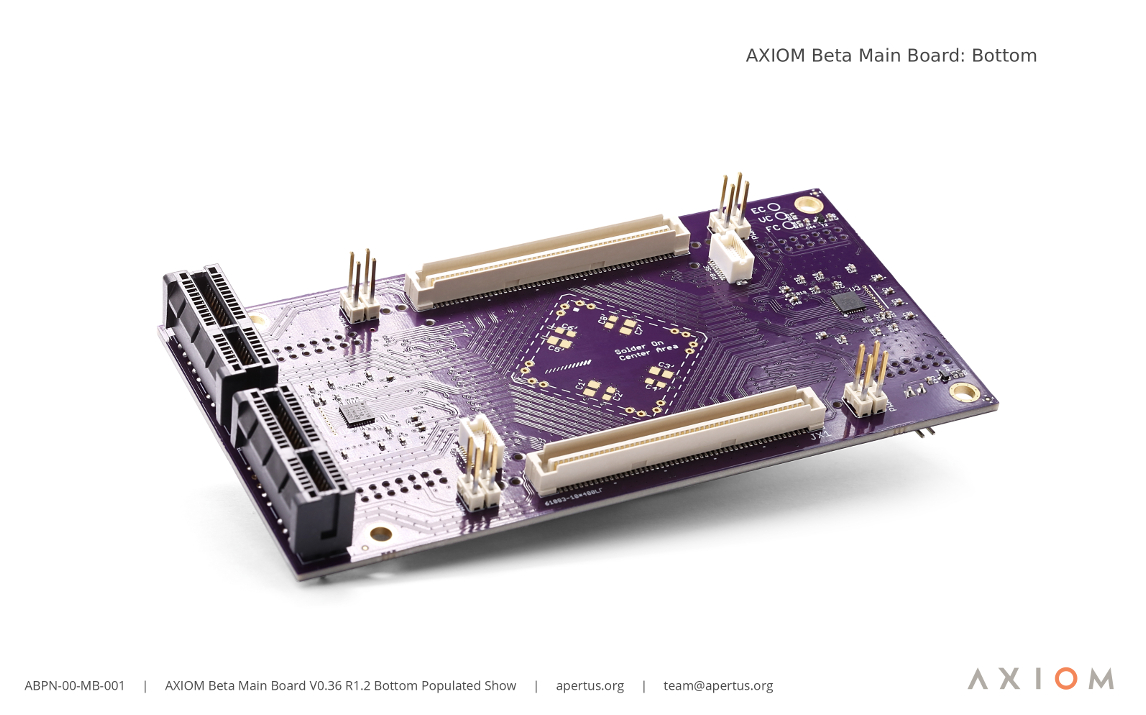

[[File: | [[File:00-MB-001- AXIOM Beta Main Board V0.36R1.2 Bottom Populated 02 Show sm b.jpg | 1150px |]] | ||

[https://wiki.apertus.org/images/2/2a/00-MB-001-_AXIOM_Beta_Main_Board_V0.36R1.2_Bottom_Populated_02_Show_b.jpg Full size image.] | |||

The Beta Main Board is | The Beta Main Board is the camera's equivalent of a PC's motherboard. Two external medium-speed shield connectors and two high-speed plugin module slots provide ample opportunity to expand other constituent parts of the camera's hardware. | ||

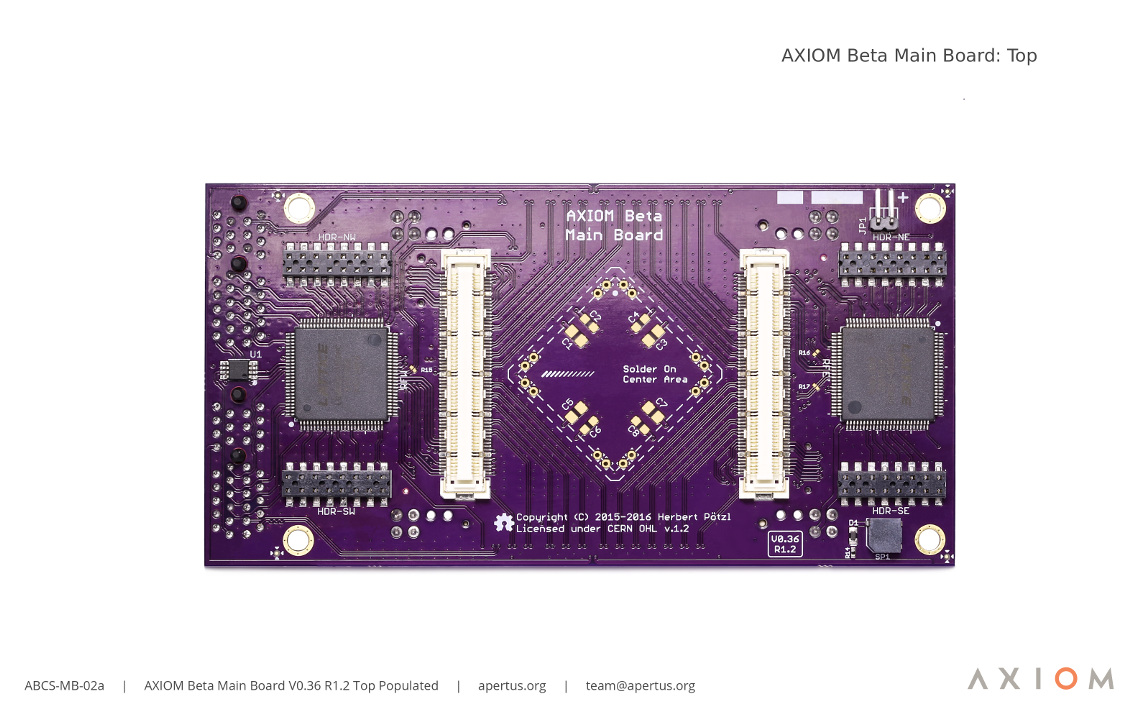

<gallery mode="packed" heights=" | [[File:ABCS-MB-02a- AXIOM Beta Main Board V0.36R1.2 Top Populated sm 02.jpg | 1150px |]] | ||

Image:Top.png| PCB | |||

Image:Bottom.png| PCB | [https://wiki.apertus.org/images/3/39/ABCS-MB-02a-_AXIOM_Beta_Main_Board_V0.36R1.2_Top_Populated_02.jpg Full size image.] | ||

In the centre of the Main Board, and on both sides of the PCB, a 'solder-on' area for [[Beta CSO]]s has been incorporated. CSOs host chips capable of, for example, sensing the camera's orientation and acceleration (the same chips used to stabilise quad-copters and track head movements in VR headsets). Being situated directly behind the image sensor's centre means that these sensors are ideally positioned to supply data surrounding image stabilisation or metadata about the camera’s orientation and movement during a shot. Two Lattice FPGAs (the so called routing fabrics) handle all the low speed GPIO communications that are required for plugin modules, shields and CSOs without sacrificing valuable Zynq GPIOs. | |||

The Main Board is positioned between the Interface Board and the Power Board in the camera's PCB stack (See [https://wiki.apertus.org/index.php/AXIOM_Beta/Camera_Structure Camera Structure]). | |||

Re: AXIOM Beta Main Board's use of Shields - [[Beta Debug Shield]] | |||

The East shield has 4 Zynq LVDS pairs, the West shield 4 Lattice LVDS pairs (both East and West shields both have 10 North and 10 South GPIOs). LVDS paired directly from the Zynq can then be considered high speed, i.e. 1Gbit/s guaranteed and up to 1.5Gbit/s under good conditions. LVDS paired from one of the Lattice FPGAs means guaranteed up to 450Mbit, i.e. under good conditions probably around 600Mbit/s. Single ended GPIOs, regardless from where they originate, are below 300MHz at best. | |||

Plugin Slots on the AXIOM Beta Main Board have 6 Zynq LVDS pairs and 8 GPIOs each, as well as one I2C bus for identification. | |||

The CSO area has 2 x 4 GPIOs which can also be used as I2C or SPI buses. | |||

[[File:ABCS-MB-02b- AXIOM Beta Main Board V0.36R1.2 Bottom Populated sm02.jpg | 1150px |]] | |||

[https://wiki.apertus.org/images/1/14/ABCS-MB-02b-_AXIOM_Beta_Main_Board_V0.36R1.2_Bottom_Populated.jpg Full size image.] | |||

<gallery mode="packed" heights="250"> | |||

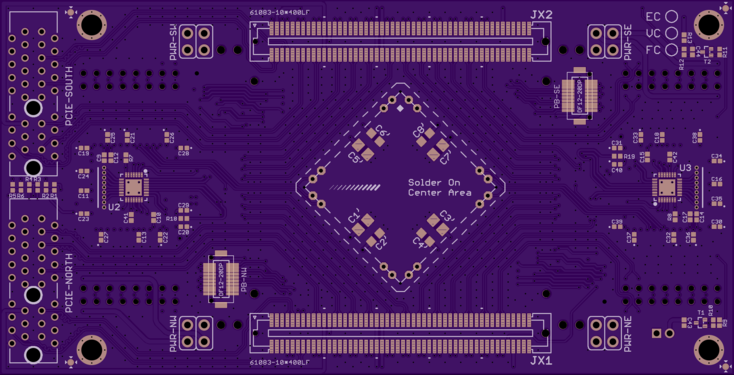

Image:Top.png| PCB Unpopulated Bottom. | |||

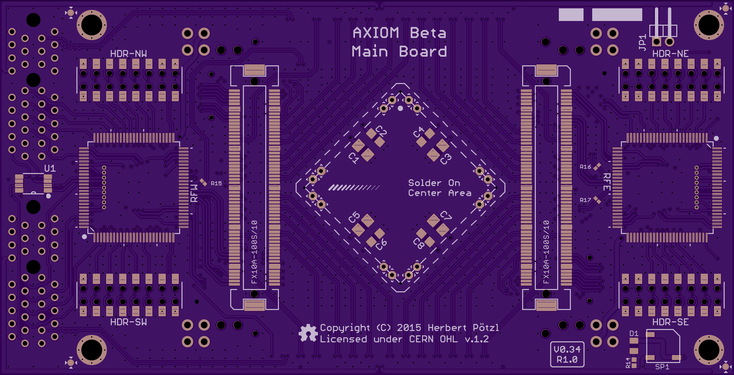

Image:Bottom.png| PCB Unpopulated Top. | |||

</gallery> | </gallery> | ||

[[AXIOM Beta | ==Programming== | ||

'''Guide to program the PIC16s in Beta Main Board''' | |||

Beta Main Board houses Microchip PIC16F1718 MCUs. We have two of these, West and East, to control Routing Fabrics West (RFW) and Routing Fabrics East (RFE) respectively. To program the PIC16s, first make sure you are connected to your [[AXIOM Beta]] either via Serial or SSH. (See [https://wiki.apertus.org/index.php/AXIOM_Beta/Manual AXIOM Beta/Manual]) | |||

<br>Run this script to prepare the MicroZed (upload a special FPGA firmware) to program the PIC16s via ICSP (Firmware 2.0): | |||

<pre>$ sudo /opt/axiom-firmware/software/bringup-scripts/prep_icsp.sh</pre> | |||

Select one of the PICs on the MUX ("A" for PIC West and "B" for PIC East) and then specify the same for <code>icsp_prog.py</code>, along with PIC's firmware hex file (Firmware 2.0): | |||

<pre style="white-space: pre-wrap"> | |||

$ sudo /opt/axiom-firmware/software/scripts/rf_sel.py A | |||

$ sudo python /opt/axiom-firmware/software/bringup-scripts/icsp_prog.py A /opt/axiom-firmware/peripherals/pic_firmware/PIC16/PIC16F1718/i2c_slave.hex | |||

$ sudo /opt/axiom-firmware/software/scripts/rf_sel.py B | |||

$ sudo python /opt/axiom-firmware/software/bringup-scripts/icsp_prog.py B /opt/axiom-firmware/peripherals/pic_firmware/PIC16/PIC16F1718/i2c_slave.hex | |||

</pre> | |||

==Current Revision== | |||

Sources: https://apertus-open-source-cinema.github.io/pcbs/index.html#/boards/AXIOM%20Beta%20Main%20Board/ | |||

[[AXIOM Beta Main Board V0.38 R1.2]] | |||

==Revision Archive== | |||

[[AXIOM Beta Main Board V0.36 R1.2]] | |||

[[AXIOM Beta Main Board V0.35]] | [[AXIOM Beta Main Board V0.35]] | ||

| Line 38: | Line 80: | ||

[[axiom beta board 100 v0.15 test]] | [[axiom beta board 100 v0.15 test]] | ||

Latest revision as of 16:55, 19 September 2023

The Beta Main Board is the camera's equivalent of a PC's motherboard. Two external medium-speed shield connectors and two high-speed plugin module slots provide ample opportunity to expand other constituent parts of the camera's hardware.

In the centre of the Main Board, and on both sides of the PCB, a 'solder-on' area for Beta CSOs has been incorporated. CSOs host chips capable of, for example, sensing the camera's orientation and acceleration (the same chips used to stabilise quad-copters and track head movements in VR headsets). Being situated directly behind the image sensor's centre means that these sensors are ideally positioned to supply data surrounding image stabilisation or metadata about the camera’s orientation and movement during a shot. Two Lattice FPGAs (the so called routing fabrics) handle all the low speed GPIO communications that are required for plugin modules, shields and CSOs without sacrificing valuable Zynq GPIOs.

The Main Board is positioned between the Interface Board and the Power Board in the camera's PCB stack (See Camera Structure).

Re: AXIOM Beta Main Board's use of Shields - Beta Debug Shield

The East shield has 4 Zynq LVDS pairs, the West shield 4 Lattice LVDS pairs (both East and West shields both have 10 North and 10 South GPIOs). LVDS paired directly from the Zynq can then be considered high speed, i.e. 1Gbit/s guaranteed and up to 1.5Gbit/s under good conditions. LVDS paired from one of the Lattice FPGAs means guaranteed up to 450Mbit, i.e. under good conditions probably around 600Mbit/s. Single ended GPIOs, regardless from where they originate, are below 300MHz at best.

Plugin Slots on the AXIOM Beta Main Board have 6 Zynq LVDS pairs and 8 GPIOs each, as well as one I2C bus for identification.

The CSO area has 2 x 4 GPIOs which can also be used as I2C or SPI buses.

1 Programming

Guide to program the PIC16s in Beta Main Board

Beta Main Board houses Microchip PIC16F1718 MCUs. We have two of these, West and East, to control Routing Fabrics West (RFW) and Routing Fabrics East (RFE) respectively. To program the PIC16s, first make sure you are connected to your AXIOM Beta either via Serial or SSH. (See AXIOM Beta/Manual)

Run this script to prepare the MicroZed (upload a special FPGA firmware) to program the PIC16s via ICSP (Firmware 2.0):

$ sudo /opt/axiom-firmware/software/bringup-scripts/prep_icsp.sh

Select one of the PICs on the MUX ("A" for PIC West and "B" for PIC East) and then specify the same for icsp_prog.py, along with PIC's firmware hex file (Firmware 2.0):

$ sudo /opt/axiom-firmware/software/scripts/rf_sel.py A $ sudo python /opt/axiom-firmware/software/bringup-scripts/icsp_prog.py A /opt/axiom-firmware/peripherals/pic_firmware/PIC16/PIC16F1718/i2c_slave.hex $ sudo /opt/axiom-firmware/software/scripts/rf_sel.py B $ sudo python /opt/axiom-firmware/software/bringup-scripts/icsp_prog.py B /opt/axiom-firmware/peripherals/pic_firmware/PIC16/PIC16F1718/i2c_slave.hex

2 Current Revision

Sources: https://apertus-open-source-cinema.github.io/pcbs/index.html#/boards/AXIOM%20Beta%20Main%20Board/

AXIOM Beta Main Board V0.38 R1.2

3 Revision Archive

AXIOM Beta Main Board V0.36 R1.2

axiom beta board 100 v0.15 test