Difference between revisions of "HDMI-Test"

(→Notes) |

|||

| (5 intermediate revisions by 2 users not shown) | |||

| Line 1: | Line 1: | ||

This page is related to the AXIOM Alpha and is outdated now. | |||

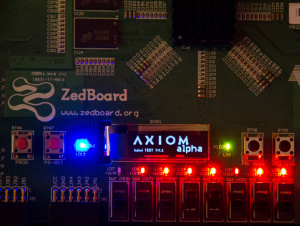

[[File:Hmdi-lcd.jpg|thumb|HDMI Test pattern generated by the FPGA displayed on an external LCD TV]] | [[File:Hmdi-lcd.jpg|thumb|HDMI Test pattern generated by the FPGA displayed on an external LCD TV]] | ||

| Line 9: | Line 11: | ||

# Boot the Zedboard | # Boot the Zedboard | ||

# After booting is complete turn switch SW3 (fifth from the left) up | # After booting is complete turn switch SW3 (fifth from the left) up | ||

# Play around with the switches to alter the generated patterns | |||

==Notes== | ==Notes== | ||

| Line 17: | Line 20: | ||

The last command will reboot the Zedboard - alternatively you can also push the right pink pushbutton on the Zedboard. | The last command will reboot the Zedboard - alternatively you can also push the right pink pushbutton on the Zedboard. | ||

==Commands== | |||

The lower 4 switches select the pattern, while the upper four modify the size: black, red, green, blue, lines h/v/both, bars h/v and checkers | |||

The idea is to check this on different displays and if necessary adjust the timing parameters | |||

There is, for example, a configuration for 1280x768 as well which can be activated by running: | |||

/usr/script/gen1280_init.sh | |||

The default 1080p mode: | |||

/usr/script/gen1920_init.sh | |||

If you unplug and replug a display, you need to execute: | |||

/usr/script/adv7511_init.sh | |||

You can adjust the pixel clock with: | |||

echo 135000000 >/sys/class/fclk/FPGA2/set_rate | |||

In 1280 mode for example you need to adjust the pixel clock to: | |||

echo 75000000 >/sys/class/fclk/FPGA2/set_rate | |||

The selected rate can be read back by typing: | |||

cat /sys/class/fclk/FPGA2/set_rate | |||

===Registers=== | |||

devmem 0x60000000 32 1664 # total width | |||

devmem 0x60000004 32 798 # total height | |||

devmem 0x60000008 32 1280 # display width | |||

devmem 0x6000000c 32 768 # display height | |||

devmem 0x60000010 32 15 # front porch | |||

devmem 0x60000014 32 2 # vertical blank | |||

devmem 0x60000018 32 1344 # h-sync start | |||

devmem 0x6000001c 32 1472 # h-sync end | |||

devmem 0x60000020 32 771 # v-sync start | |||

devmem 0x60000024 32 778 # v-sync end | |||

devmem 0x60000028 32 41 # pattern size | |||

[[Category:Project]] | [[Category:Project]] | ||

[[Category:Zedboard]] | [[Category:Zedboard]] | ||

Latest revision as of 08:08, 9 April 2024

This page is related to the AXIOM Alpha and is outdated now.

- Format an SD card with one vfat partition (this is the default for the SD card that comes with the Zedboard)

- Download http://vserver.13thfloor.at/Stuff/AXIOM/ALPHA/axiom_alpha_hdmi_test_v0.1.zip and put all the files in the zipped folder onto your SD card (not into a subfolder)

- Connect a monitor to the Zedboards HDMI port and turn on the monitor.

- Shift all switches on the Zedboard down

- Boot the Zedboard

- After booting is complete turn switch SW3 (fifth from the left) up

- Play around with the switches to alter the generated patterns

1 Notes

If the Zedboard is booting via TFTP by default use an UART / serial console and interrupt the bootloader then type:

env default -f saveenv reset

The last command will reboot the Zedboard - alternatively you can also push the right pink pushbutton on the Zedboard.

2 Commands

The lower 4 switches select the pattern, while the upper four modify the size: black, red, green, blue, lines h/v/both, bars h/v and checkers

The idea is to check this on different displays and if necessary adjust the timing parameters

There is, for example, a configuration for 1280x768 as well which can be activated by running:

/usr/script/gen1280_init.sh

The default 1080p mode:

/usr/script/gen1920_init.sh

If you unplug and replug a display, you need to execute:

/usr/script/adv7511_init.sh

You can adjust the pixel clock with:

echo 135000000 >/sys/class/fclk/FPGA2/set_rate

In 1280 mode for example you need to adjust the pixel clock to:

echo 75000000 >/sys/class/fclk/FPGA2/set_rate

The selected rate can be read back by typing:

cat /sys/class/fclk/FPGA2/set_rate

2.1 Registers

devmem 0x60000000 32 1664 # total width devmem 0x60000004 32 798 # total height devmem 0x60000008 32 1280 # display width devmem 0x6000000c 32 768 # display height devmem 0x60000010 32 15 # front porch devmem 0x60000014 32 2 # vertical blank devmem 0x60000018 32 1344 # h-sync start devmem 0x6000001c 32 1472 # h-sync end devmem 0x60000020 32 771 # v-sync start devmem 0x60000024 32 778 # v-sync end devmem 0x60000028 32 41 # pattern size